# **Chapter 10**

# **Circuits**

#### **Contents**

| 10.1 Int  | oduction                                                                        |

|-----------|---------------------------------------------------------------------------------|

| 10.1      | .1 Length, mass, and time in the SI system                                      |

| 10.1      | .2 Electric charge, energy, power, and potential in the SI system               |

| 10.1      | .3 Fundamental analog circuit elements                                          |

| 10.1      | .4 Kirchoff's laws                                                              |

| 10.1      | .5 Laplace transform analysis of circuits and the definition of impedance 10-13 |

| 10.2 Act  | ive analog circuits & filters                                                   |

| 10.2      | .1 Semiconductor circuit elements                                               |

| 10.3 Ope  | erational amplifiers                                                            |

| 10.3      | .1 Design and analysis of a few useful op amp circuits                          |

| 10.4 Sign | nal transmission                                                                |

| 10.4      | .1 Digital logic and storage elements                                           |

| 10.4      | .2 Telegrapher's equation and characteristic impedance                          |

|           | s                                                                               |

# 10.1 Introduction

## 10.1.1 Length, mass, and time in the SI system

From basic mechanics, the reader should already be familiar with the fundamental units of {length, mass, time} as {meter (m), kilogram (kg), second (s)} in the International System of Units (SI, the modern form of the metric system), as well as several derived units, such as force (newton,  $N = kg \, m/s^2$ ), pressure (pascal,  $Pa = kg/m/s^2$ ), energy or work (joule,  $J = N \, m$ ), power (watt, W = J/s), frequency (hertz, Hz = 1/s), speed (m/s), acceleration (m/s²), angular velocity (rad/s) and acceleration (rad/s²), momentum (N s), angular momentum (N m s), torque (N m), etc. Recall also the usual prefixes of the SI system (cf. the binary powers in Table 1.1):

|                    |           |           |           |           |           |            | femto      |            |            |            |

|--------------------|-----------|-----------|-----------|-----------|-----------|------------|------------|------------|------------|------------|

| symbol:<br>factor: | d         | С         | m         | $\mu$     | n         | р          | f          | a          | Z          | У          |

| factor:            | $10^{-1}$ | $10^{-2}$ | $10^{-3}$ | $10^{-6}$ | $10^{-9}$ | $10^{-12}$ | $10^{-15}$ | $10^{-18}$ | $10^{-21}$ | $10^{-24}$ |

|                    |           | _         |           |           | •         |            |            | •          |            |            |

|                    |           |           |           |           |           |            | peta       |            |            |            |

| symbol:<br>factor: | da        | h         | k         | М         | G         | Т          | Р          | E          | Z          | Y          |

| -                  | II        |           |           |           | 1.00      | 4 0 1 9    | 4 0 15     | 4 0 1 0    | 4 0 0 1    | 4 0 9 4    |

### 10.1.2 Electric charge, energy, power, and potential in the SI system

The SI units of the various quantities encountered in electric circuits is now summarized:

- **Charge** is denoted q. The fundamental unit of charge is that of an electron; the (negative) charge of  $6.2415 \times 10^{18}$  electrons is called a **coulomb** (C), which is the SI unit for charge.

- Electric charge passing a given point per unit time is called **current**. The current at any instant is denoted I = dq/dt. The SI unit for current is the **ampere** (A, a.k.a. **amp**), which is a flow of 1 C/s.

- **Energy** (aka **work**) is denoted w, and the SI unit for (mechanical or electrical) energy is the **joule** (J). In mechanical terms, a joule of energy is 1 kg m<sup>2</sup>/s<sup>2</sup>, which may be interpreted as 1 N m when applying a force to a mass over a distance, or as 0.2390 calories of thermal energy, where 1 **calorie** (cal) is the amount of thermal energy it takes to warm 1 g (that is, 1 mL, or 1 cm<sup>3</sup>) of water by 1°C at standard atmospheric conditions. Electric energy, also measured in joules, is the electric equivalent, as electrical energy can easily be converted to heat, or to mechanical energy (to apply a force over a distance) plus heat.

- **Power** is the rate of change of energy at any instant (that is, energy is the integral of power over time), and is denoted P = dw/dt; the SI unit for power is the **watt** (W), which is 1 J/s. In mechanical terms, a watt of power is 1 kg m<sup>2</sup> / s<sup>3</sup>, which may be interpreted as 1 N m/s when applying a force to a mass moving at a certain speed, or as 0.2390 cal/s when warming a material.

- In an electric circuit, associated with any electron is its potential to do work<sup>1</sup> relative to some convenient (yet, arbitrarily-defined) base state, called the **ground** state. This definition is analogous to the gravitational potential energy associated with any mass at any given height relative to an (arbitrarily-defined) gravitational ground state. The **potential** of a charge to do work, also called the **voltage** of this charge, is denoted V = dw/dq, and is defined analogously, relative to an (arbitrarily-defined) electrical ground state. The SI unit for potential is the **volt** (V), which is 1 J / C.

Via the above definitions and the chain rule for differentiation, it follows immediately that

$$P = \frac{dw}{dt} = \frac{dw}{dq}\frac{dq}{dt} \quad \Rightarrow \quad \boxed{P = VI}$$

(10.1)

Current may be envisioned as a flow of electrons, as described above; however, by convention, the (positive) direction of the current is defined as the direction *opposite* to the flow of electrons. This is known as the **passive sign convention**. Using this (at first, somewhat peculiar<sup>2</sup>) convention, when considering the voltage V across a device and the current I through a device, multiplying V times I as suggested by (10.1) results in

- positive power P if the device absorbs electric power from the rest of the circuit, as in a resistor<sup>3</sup>, with current flowing from higher voltage to lower voltage, and

- *negative* power *P* if the device *delivers* electric power to the rest of the circuit, as in a battery, with current flowing from *lower* voltage to *higher* voltage.

As a departure from the SI convention, on the electric grid of a city, energy is usually billed in **kilowatt hours** (kW h) instead of megajoules (MJ); note that 1 kW h = 3.6 MJ. Similarly, battery charge is usually measured as **milliamp hours** (mA h) instead of coulombs (C); note that 1 mA h = 3.6 C.

<sup>&</sup>lt;sup>1</sup>As an example, consider two identical metal spheres, one with an excess of electrons (said to be of lower voltage), and one with a depletion of electrons (said to be of higher voltage). If a resistor is connected between the two spheres, the excess repulsive force between the electrons on the first sphere tends to push electrons through the resistor and onto the second sphere until a balanced distribution of electrons is reached. In the process, the electrons being pushed through the resistor do work, generating heat.

<sup>&</sup>lt;sup>2</sup>The reason for this peculiar convention is that the fundamental charge associated with an electron is defined as being *negative*; this definition was made early on, and it stuck.

<sup>&</sup>lt;sup>3</sup>The power absorbed may be converted into **heat**, as in a resistor, a combination of **heat & electromagnetic radiation**, as in a lightbulb, laser, or RF transmitter, a combination of **heat & mechanical power**, as in a motor, fluid pump, or speaker coil, etc., or it may alternatively be *stored* (and, later, released), as in a capacitor or inductor (see §10.1.3.1), a rechargeable battery, a flywheel, etc.

The change of energy of a single electron if it is moved across a potential difference of one volt is defined as an **electron volt** (eV), and is given by  $1/(6.2415 \times 10^{18}) = 1.6022 \times 10^{-19}$  J. Note that the energy E of a **photon** is given by  $E = hc/\lambda$ , where **Planck's constant**  $h = 6.626 \times 10^{-34}$  J s and the **speed of light**  $c = 2.99792 \times 10^8$  m/s; thus, if a single electron moves across a 1.91 V potential difference, then releases its excess energy as a photon, the resulting photon has wavelength  $\lambda = 650$  nm, and is thus red in color.

## 10.1.3 Fundamental analog circuit elements

#### 10.1.3.1 Resistors, capacitors, & inductors

Idealized current-voltage relationships for three common devices<sup>4</sup> used in analog circuits are

resistor (denoted

$$\longrightarrow$$

):  $V = RI$   $\Rightarrow P_R = VI = I^2 R = V^2/R \ge 0,$  (10.2a)

capacitor (denoted — ):

$$I = C dV/dt$$

$\Rightarrow P_C = VI = (C/2) dV^2/dt = dw_C/dt$ , (10.2b)

inductor (denoted

$$\sim \sim$$

):  $V = L \ dI/dt$   $\Rightarrow P_L = VI = (L/2) \ dI^2/dt = dw_L/dt$ , (10.2c)

where  $w_C = C V^2/2$  and  $w_L = L I^2/2$ . Approximate values of R, C, and L for such devices are identified with **color bands** or **numerical codes**, the interpretation of which are easy to find online. Note that:

- The SI unit for resistance R is the **ohm** ( $\Omega$ ) [thus, (10.2a) is known as **Ohm's law**]; an ohm is 1 V / A.

- The SI unit for capacitance C is the **farad** (F); a farad is 1 A s / V.

- The SI unit for inductance L is the **henry** (H); a henry is 1 V s / A.

When operating, electric power is always *absorbed* (i.e., dissipated as heat) by a resistor, but at any instant may either be *absorbed from* or *delivered to* the rest of the circuit by a capacitor or inductor [see (10.2)].

The idealized linear models listed above are accurate only for sufficiently small V and I inside what are known as the **rated limits** of the corresponding device; outside these limits, nonlinearities become significant (and, far outside these limits, the corresponding device will fail).

The flow of electrons along a metal wire, like that of water through a pipe, is almost always<sup>5</sup> associated with some loss of potential per unit length (and, therefore, some resistance), as energy is lost as heat to sustain the flow when the magnetic fields generated by the flowing electrons interact with the electromagnetic fields of the atoms within the material. Wires are simply made from an appropriate metal, like copper, with relatively low (often, negligible) resistance per unit length, whereas resistors are made from an appropriate metal, like Nichrome (a non-magnetic alloy of nickel and chromium), that exhibits a relatively high resistance per unit length, with a resistance that is fairly insensitive to the inevitable temperature fluctuations caused by driving a current through a resistor. Note that, when running a large current through a resistor, the metal warms up, and thus atoms within the metal start vibrating more energetically; this generally reduces the effective resistance R of the resistor when |I| is large, eventually leading to a nonlinear relationship between V and I [cf. (10.2a)].

Though they are packaged in a variety of compact geometries, *capacitors* are perhaps best visualized as two parallel metal plates with a nonconducting material, called a **dielectric**, between them. If a current is directed through a capacitor, electrons flow in one wire and accumulate on one of the plates, repelling the electrons on the other (nearby) plate, which then flow out the other wire. As electrons accumulate on the first plate and are depleted from the second, an *electric potential difference* is gradually built up, thus inhibiting the further flow of electrons; at steady state, the current through the capacitor therefore reduces to zero.

<sup>&</sup>lt;sup>4</sup>As suggested by Thomas & Rosa (2010), we will refer to the physical hardware components that a circuit is made from as **devices**, and the equations we use to model them as **elements**.

<sup>&</sup>lt;sup>5</sup>The exception to this statement is the remarkable class of materials known as **superconductors**, which at temperatures below a material-dependent critical temperature exhibit **zero resistance** and the expulsion of magnetic fields from within the material.

The resulting (linearized) relationship between between V and I is given in (10.2b). As shown in (10.2b), the power absorbed by or released from a capacitor at any instant,  $P_C$ , is simply the rate of change of the energy,  $w_C = C \, V^2/2$ , stored<sup>6</sup> in the capacitor, where V is the voltage across the capacitor, which quantifies the accumulated charge difference across its two plates. Further, if the current through the capacitor is  $I = \cos(\omega t) = \sin(\omega t + \pi/2)$ , then the voltage across the capacitor is  $V = (1/C)\sin(\omega t)/\omega$  [the voltage "lags" behind the current by  $\pi/2$ , and its magnitude reduces like  $1/\omega$ , as the charge difference between the two sides of the capacitor takes time to accumulate; think of the current variation as the "cause", and the voltage variation as the "effect"]. The absorbed power  $P_C$ , averaged over any multiple of periods  $T = 2\pi/\omega$ , is exactly zero.

Conversely, inductors are perhaps best visualized as tightly-wound (often, toroidal) copper wire coils wrapped around an air or (better) a ferromagnetic **core**; when a current flows through the wire, a compatible magnetic field is maintained within this core. If a voltage is applied across an inductor, the existing magnetic field in the core, or lack thereof, exerts an electromotive force on the flow of electrons which initially opposes a corresponding change in the current. As a voltage difference is maintained across the inductor (which, in turn, is generated by the circuit that is connected to it), the current through the inductor, and the corresponding magnetic field, grows in response; at steady state, the voltage across the inductor reduces to zero? The resulting (linearized) relationship between between V and I is given in (10.2c). As shown in (10.2c), the power absorbed by or released from an inductor at any instant,  $P_L$ , is simply the rate of change of the energy,  $w_L = L I^2/2$ , stored? in the inductor, where I is the current through the inductor, which quantifies the accumulated magnetic field through its core. Further, if the voltage across an inductor is  $V = \cos(\omega t) = \sin(\omega t + \pi/2)$ , then the current through the inductor is  $I = (1/L)\sin(\omega t)/\omega$  [the current "lags" behind the voltage by  $\pi/2$ , and its magnitude reduces like  $1/\omega$ , as the magnetic field within its core takes time to accumulate, and the corresponding electromotive force opposes a change in the current; think of the voltage variation as the "cause", and the current variation as the "effect"]. The absorbed power  $P_L$ , averaged over any multiple of periods  $T = 2\pi/\omega$ , is exactly zero.

The prepackaged resistors, capacitors, and inductors that are commercially available are manufactured with significant variation. Resistors are commonly available with the following tolerances on their nominal resistance:  $\{\pm20\%,\,\pm10\%,\,\pm5\%,\,\pm2\%,\,\pm1\%,\,\pm0.5\%,\,\pm0.25\%,\,\pm0.25\%,\,\pm0.1\%\}.$  Associated with each of these tolerance levels is a family of resistance values denoted Ex, where x is the number of resistance values per decade that are available in that family, as listed in Tables 10.1-10.6. Available resistors in, e.g., the E6 family include 1.0 k $\Omega$ , 1.5 k $\Omega$ , 2.2 k $\Omega$ , 3.3 k $\Omega$ , 4.7 k $\Omega$ , 6.8 k $\Omega$ , 10 k $\Omega$ , 15 k $\Omega$  etc. The process of converting (rounding up or down) a given resistance to a value in one of these families is, of course, easily automated (see RR\_common\_resistor\_values.m). Note that higher-precision resistors are more expensive and less commonly stocked at PCB fabrication facilities, and should be avoided. Note also that **calibration** may be used to eliminate the error associated with the use of lower-precision (less expensive) resistors in, e.g., voltage divider circuits, as discussed in §5.7.4.

Resistors at various tolerance levels are often produced as the result of a single manufacturing process, then tested to determine their precise resistance (using, for example, the Wheatstone bridge circuit analyzed in Example 10.5). They are then binned accordingly and, of course, those resistors most closely matching the target resistance of the higher-precision class sold at a higher price. The result of this manufacturing/sorting process is that the distribution of the actual resistance of those resistors marked at, say, 2% tolerance are often **bimodal**, as those units that more accurately match target resistance values at 1% tolerance are not placed in the higher-tolerance (2%) bins. The manufacture of (more expensive) high-precision resistors is often accomplished by accurate **laser trimming** of resistors that are initially slightly below the target resistance.

<sup>&</sup>lt;sup>6</sup>A mechanical spring stores and releases the energy associated with its compression; as a rough analog, a capacitor can be thought of as a sort of "spring" on the voltage, storing and releasing the energy associated with an accumulated charge, whereas an inductor can be thought of as a "spring" on the current, storing and releasing the energy associated with an accumulated magnetic field.

<sup>&</sup>lt;sup>7</sup>As a mnemonic, a *capacitor has low voltage across it at high frequencies*, as electric charge doesn't have enough time build up on it, whereas an *inductor has low current through it at high frequencies*, as a compatible magnetic field doesn't have time to form.

#### 1.0 1.5 2.2 3.3 4.7 6.8

Table 10.1: The 6 resistance values per decade in the **E6** family of  $\pm 20\%$  tolerance resistors.

1.0 1.2 1.5 1.8 2.2 2.7 3.3 3.9 4.7 5.6 6.8 8.2

Table 10.2: The 12 resistance values per decade in the **E12** family of  $\pm 10\%$  tolerance resistors.

1.1 1.2 1.3 1.5 1.6 1.8 2.0 2.2 2.4 2.7 3.0 3.6 3.9 4.3 4.7 5.1 5.6 6.2 6.8 7.5 9.1 3.3 8.2

Table 10.3: The 24 resistance values per decade in the **E24** family of  $\pm 5\%$  tolerance resistors.

1.00 1.10 1.15 1.21 1.27 1.33 1.40 1.47 1.54 1.62 1.69 1.78 2.05 1.05 1.87 1.96 2.15 2.26 2.37 2.49 2.87 3.32 3.48 3.65 3.83 2.61 2.74 3.01 3.16 4.02 4.22 4.42 5.90 7.15 7.50 4.64 4.87 5.11 5.36 5.62 6.19 6.49 6.81 7.87 8.25 8.66 9.09 9.53

Table 10.4: The 48 resistance values per decade in the **E48** family of  $\pm 2\%$  tolerance resistors.

1.30 1.00 1.02 1.05 1.07 1.10 1.13 1.15 1.18 1.21 1.24 1.27 1.33 1.37 1.40 1.43 1.47 1.50 1.54 1.58 1.62 1.65 1.69 1.74 1.78 1.82 1.87 1.91 1.96 2.00 2.05 2.10 2.21 2.26 2.32 2.37 2.43 2.49 2.55 2.61 2.67 2.74 2.80 2.87 3.01 3.09 2.15 2.94 3.16 3.24 3.32 3.40 3.48 3.57 3.65 3.74 3.83 3.92 4.02 4.12 4.22 4.32 4.42 4.53 5.23 5.36 5.62 5.76 5.90 6.04 6.19 6.49 4.64 4.75 4.87 4.99 5.11 5.49 6.34 6.65 9.09 6.81 6.98 7.15 7.32 7.50 7.68 7.87 8.06 8.25 8.45 8.66 8.87 9.31 9.53 9.76

Table 10.5: The 96 resistance values per decade in the **E96** family of  $\pm 1\%$  tolerance resistors.

1.20 1.00 1.01 1.02 1.04 1.05 1.06 1.07 1.09 1.10 1.11 1.13 1.14 1.15 1.17 1.18 1.21 1.23 1.24 1.26 1.27 1.29 1.30 1.32 1.33 1.35 1.37 1.38 1.40 1.42 1.43 1.45 1.47 1.49 1.50 1.52 1.54 1.56 1.58 1.62 1.64 1.65 1.67 1.69 1.72 1.74 1.76 1.60 1.78 1.80 1.82 1.84 1.87 1.89 1.91 1.93 1.96 1.98 2.00 2.03 2.05 2.08 2.10 2.13 2.18 2.21 2.23 2.26 2.29 2.32 2.34 2.37 2.40 2.43 2.46 2.49 2.52 2.55 2.58 2.15 2.61 2.64 2.67 2.71 2.74 2.77 2.80 2.84 2.87 2.91 2.94 2.98 3.01 3.05 3.09 3.12 3.16 3.20 3.24 3.28 3.32 3.36 3.40 3.44 3.48 3.52 3.57 3.61 3.65 3.70 3.74 3.79 3.83 3.88 3.92 3.97 4.02 4.07 4.12 4.17 4.22 4.27 4.32 4.37 4.42 4.48 4.53 4.59 4.70 4.87 4.93 4.99 5.05 5.11 5.17 5.23 5.30 5.36 5.56 4.64 4.75 4.81 5.42 5.49 5.76 5.83 5.90 5.97 6.04 6.12 6.19 6.26 6.34 6.42 6.49 6.73 5.62 5.69 6.57 6.65 6.98 7.06 7.15 7.23 7.32 7.50 7.59 7.68 7.77 7.87 7.96 8.06 8.16 6.81 6.90 7.41 8.35 8.45 8.56 8.66 8.76 8.87 8.98 9.09 9.20 9.31 9.42 9.53 9.65 9.76 9.88

Table 10.6: The resistance values in the **E192** families of  $\pm 0.5\%$ ,  $\pm 0.25\%$ , and  $\pm 0.1\%$  tolerance resistors.

Capacitors are commonly available from 1 pF through 10 nF in 24 capacitance values per decade (coinciding in values with the E24 series in Table 10.3), and from 10 nF=0.01  $\mu$ F through 10 mF= $10^4$   $\mu$ F in 6 capacitance values per decade (coinciding in values with the E6 series in Table 10.1). Inductors are commonly available from 1 nH through 1 mH in 24 inductance values per decade (coinciding in values with the E24 series in Table 10.3). Capacitors and inductors in the higher ends of these ranges are both large and expensive; increased voltage ratings on capacitors, and increased current ratings on inductors, also increase their size and cost significantly.

#### 10.1.3.2 Power sources

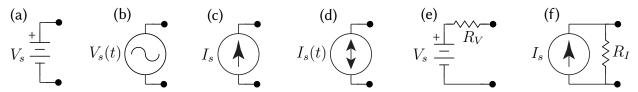

In order to make an electric circuit do something, of course, you need a source<sup>9</sup> of electric power. Such sources come in two types, voltage sources (which are most common) and current sources, either of which may drive the connected circuit in a constant or time-varying manner, and are denoted as indicated in Figure 10.1a-d.

<sup>&</sup>lt;sup>8</sup>Time constants in RLC circuits (incorporating resistors, inductors, and capacitors) may be tuned by selecting the resistors in the circuit (see, e.g., Example 10.2), so a finer granularity in available values per decade is not necessary for capacitors and inductors.

<sup>&</sup>lt;sup>9</sup>Note that some devices that normally act as *sources* of electric power, like rechargeable batteries, may also from time to time be used safely as *sinks* of electric power, like a capacitor. The practical distinction between a capacitor and a rechargeable battery is that a capacitor, which simply stores and releases electrons, typically loses its charge fairly quickly when not being used, whereas a battery, which stores and releases charge via internal chemical reactions, typically holds its charge for much longer periods of time.

Figure 10.1: Various power sources, and the symbols used for them in this text: (a) ideal constant-voltage source, (b) ideal time-varying voltage source, (c) ideal constant-current source, (d) ideal time-varying current source, (e) practical constant-voltage source, (f) practical constant-current source.

Figure 10.2: Current-voltage relationship of (left) the practical voltage source of Figure 10.1e, and (right) the practical current source of Figure 10.1f.

The current-voltage relationships of ideal voltage and current sources may be written

ideal voltage source:

$$V = V_s$$

(regardless of  $I$ ) ideal current source:  $I = I_s$  (regardless of  $V$ ) (10.2d)

Note that an ideal **voltage source** generates a specified *voltage* across its terminals <sup>10</sup> regardless of the current drawn by the rest of the circuit; an ideal voltage source can not function correctly if a wire (with zero resistance) is connected across its terminals (a.k.a. a **short circuit**), as that would cause the ideal voltage source to produce infinite current. Similarly, an ideal **current source** generates a specified *current* through the device(s) connected across its terminals regardless of the voltage required over the rest of the circuit in order to maintain it; an ideal current source can not function correctly if the circuit connected across its terminals is not closed (a.k.a. an **open circuit**), as that would cause the ideal current source to produce infinite voltage.

Despite the above-mentioned limitations, ideal voltage and current sources are reasonably good models in many situations when a circuit is properly configured. More accurate (yet still linear) models of real-world voltage and current sources are indicated in Figure 10.1e-f. In these more practical models,

- a (preferably, small) resister  $R_V$  is included in *series* with the voltage source, which thus generates a finite current of  $I = V_s/R_V$ , instead of an infinite current, in the case of a short circuit across its terminals, and

- a (preferably, large) resister  $R_I$  is included in *parallel* with the current source, which thus generates a finite voltage of  $V = I_s R_I$ , instead of an infinite voltage, in the case of a open circuit across its terminals.

The current-voltage relationship of the practical voltage and current sources indicated in Figures 10.1e-f are given in Figure 10.2. Note that, taking  $I_s = V_s/R_V$  and  $R_I = R_V$ , these two relationships are identical, and thus these two sources are, consistent with the following definition, said to be<sup>11</sup> "equivalent".

**Fact 10.1 (Equivalent circuit definition)** Two circuits are said to be **equivalent** at a specified pair of terminals if they exhibit an identical current-voltage relationship, which may be static or dynamic.

<sup>&</sup>lt;sup>10</sup>Note that a **terminal** of an electric circuit or individual circuit element is a point at which other electric circuits are intended to be attached, as denoted by black dots in Figure 10.1.

<sup>&</sup>lt;sup>11</sup>Though these two practical source models are "equivalent" from the perspective of the current-voltage relationship at their terminals, they are **not at all equivalent** in terms of their internal operation:

<sup>•</sup> a practical voltage source (e.g., a common battery) expends essentially no power whatsoever if there is an *open* circuit across its terminals (since the current through, and therefore the power consumed by, its internal resistor is zero in this case), but it expends significant power if there is a *short* circuit across its terminals (since the power consumed by its internal resistor in this case is  $P = V_s I$ , where  $I = V_s / R_V$  for small  $R_V$ );

#### 10.1.3.3 Sensors & actuators for interfacing with the physical world

To connect an electric circuit to the physical world, sensors and actuators <sup>12</sup> are needed, as surveyed in §6. Actuators are often built from some type of **electric motor** (see §6.8-6.11); others include **linear actuators** (like **voice coils**), **electroactive polymers**, etc. Common sensors include **accelerometers** (**accels**) to measure linear acceleration, **gyroscopes** (**gyros**) to measure angular acceleration, **encoders** to measure wheel rotation, **thermocouples** to measure temperature, etc. Note that some actuators which convert electrical energy to mechanical energy (like motors and piezoelectric actuators <sup>13</sup>) can also be used as sensors or **energy scavengers** to convert mechanical energy back into electrical energy (like generators and piezoelectric sensors <sup>13</sup>); this concept is central to the efficient operation of hybrid and fully electric cars, in which the motor normally used to drive the wheels may be operated as a generator during regenerative braking.

#### 10.1.4 Kirchoff's laws

A **node** of an electric circuit is defined as any point at which two or more circuit elements (and, thus, two or more current paths) are connected. In a complex electric circuit with several circuit elements and several current paths, the following two simple rules facilitate analysis:

Fact 10.2 (Kirchoff's Current Law, or KCL) The sum of the currents entering a node equals the sum of the currents leaving that node at any instant.

Fact 10.3 (Kirchoff's Voltage Law, or KVL) The sum of the voltages across the elements around any closed loop in a circuit is zero at any instant.

Note that KVL may be satisfied by construction, simply by keeping track of the voltage at each node of the circuit, rather than the voltage drop across each circuit element. Note also that, in a circuit with n nodes, there are only (n-1) independent KCL equations for the currents between these nodes, as the KCL at the last node may be derived by combining appropriately the KCL relations at the other (n-1) nodes.

Defining the voltage at each node (thus implicitly satisfying the KVL equations) and the current between each node, writing KCL at all but one of the nodes, and writing the current-voltage relationship across each circuit element [see, e.g., (10.2a)-(10.2d)] leads to a set of ODEs which, together with the initial conditions, completely describe the time evolution of the circuit. This is best illustrated by a few examples.

**Example 10.1 Voltage divider**. Consider first a simple circuit formed as a series connection of two resistors,  $R_1$  and  $R_2$ , with an ideal voltage source applied between the first node  $V_1$  and the last node  $V_2$ , and denote by  $V_{\text{mid}}$  the voltage at the middle node. Since the current through the first resistor equals the current through the second resistor by KCL, applying (10.2a) leads immediately to

$$I_1 = I_2 \quad \Rightarrow \quad \frac{V_1 - V_{\text{mid}}}{R_1} = \frac{V_{\text{mid}} - V_2}{R_2} \quad \Rightarrow \quad V_{\text{mid}} = \frac{R_2 \, V_1 + R_1 \, V_2}{R_1 + R_2}.$$

It is seen that  $V_{\text{mid}} = (V_1 + V_2)/2$  if  $R_1 = R_2$ , that  $V_{\text{mid}} \to V_1$  if  $R_1 \ll R_2$ , and that  $V_{\text{mid}} \to V_2$  if  $R_2 \ll R_1$ .  $\triangle$

<sup>•</sup> in contrast, a practical current source (e.g., as developed in Examples 10.15 and 10.16) expends essentially no power whatsoever if there is a *short* circuit across its terminals (since the voltage across, and therefore the power consumed by, its internal resistor is zero in this case), but it expends significant power if there is an *open* circuit across its terminals (since the power consumed by its internal resistor in this case is  $P = V I_s$ , where  $V = I_s R_I$  for large  $R_I$ ).

<sup>&</sup>lt;sup>12</sup>More broadly, devices which convert one form of energy (electric, mechanical, thermal, etc.) to another are called transducers.

<sup>&</sup>lt;sup>13</sup>That is, actuators/sensors built on materials exhibiting the **piezoelectric effect**, generating an electric field in response to applied mechanical strain, and the **reverse piezoelectric effect**, generating mechanical strain in response to an applied electric field.

(a)

$$V_i(t) \bullet \longrightarrow V_o(t)$$

(b)  $V_i(t) \bullet \longrightarrow V_o(t)$  (c)  $V_s \bullet V_o(t)$  (d)  $V_i(t) \bullet \longrightarrow V_o(t)$   $V_i(t) \bullet \longrightarrow V_o(t)$   $V_i(t) \bullet \longrightarrow V_o(t)$   $V_i(t) \bullet \longrightarrow V_o(t)$

Figure 10.3: Four simple passive filters: (a) a first-order low-pass RC filter, (b) a first-order high-pass RC filter, (c) a voltage-biased first-order high-pass RC filter, and (d) a second-order low-pass LC filter.

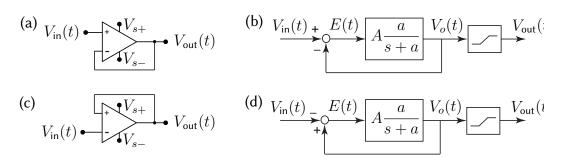

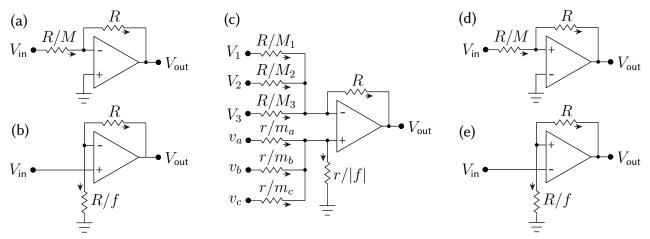

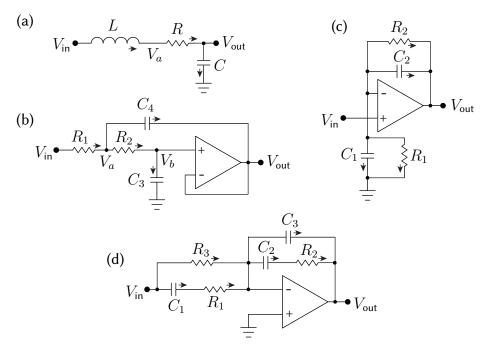

**Example 10.2 Passive filters.** Consider now the four circuits shown in Figures 10.3a-c, and assume that

- (a) the input voltage  $V_i(t)$  is precisely specified regardless of the current drawn by the filter, and

- (b) the current, if any, out the output terminal [marked  $V_o(t)$  in the figure] is negligible.

It follows (see code in RR Chapter 10) that the first-order low-pass RC filter in Figure 10.3a is governed by

$$I_R = I_C, \quad V_i - V_o = I_R R, \quad I_C = C \frac{d V_o}{dt} \quad \Rightarrow \quad V_i(s) - V_o(s) = R C s V_o(s) \quad \Rightarrow \quad \frac{V_o(s)}{V_i(s)} = \frac{\omega_1}{s + \omega_1}$$

where  $\omega_1 = 1/(RC)$ , the **first-order high-pass RC filter** in Figure 10.3b is governed by

$$I_C = I_R, \quad I_C = C \frac{d[V_i - V_o]}{dt}, \quad V_o = I_R R \quad \Rightarrow \quad R C s \left[V_i(s) - V_o(s)\right] = V_o(s) \quad \Rightarrow \quad \frac{V_o(s)}{V_i(s)} = \frac{s}{s + \omega_1},$$

the voltage-biased first-order high-pass RC filter in Figure 10.3c is governed by

$$\begin{split} I_C + I_1 &= I_2, \quad I_C = C \, \frac{d[V_i - V_o]}{dt}, \quad (V_s - V_o) = I_1 \, R_1, \quad V_o = I_2 \, R_2 \quad \Rightarrow \\ V_o(s) &= \frac{R_2 \, V_s}{R_1 + R_2 + R_1 \, R_2 \, C \, s} + \frac{R_1 \, R_2 \, C \, s \, V_{\rm i}(s)}{R_1 + R_2 + R_1 \, R_2 \, C \, s} = \frac{R_2}{R_1 + R_2} \, \frac{\omega_2}{s + \omega_2} \, V_s + \frac{s}{s + \omega_2} \, V_{\rm i}(s) \end{split}$$

where the effective resistance  $R_e$  is  $R_e = R_1 R_2/(R_1 + R_2)$  [that is,  $1/R_e = 1/R_1 + 1/R_2$ ] and  $\omega_2 = 1/(R_e C)$ , and the **second-order low-pass LC filter** in Figure 10.3d is governed by

$$I_L = I_C, \quad V_i - V_o = L \frac{d[I_L]}{dt}, \quad I_C = C \frac{dV_o}{dt} \quad \Rightarrow \quad V_i(s) - V_o(s) = L C s^2 V_o(s) \quad \Rightarrow \quad \frac{V_o(s)}{V_i(s)} = \frac{\omega_3^2}{s^2 + \omega_3^2}$$

where  $\omega_3 = 1/\sqrt{L\,C}$ . Assumptions (a) and (b) above are quite restrictive, however: if the inputs of such **passive filters** are attached to real sensors, if they are cascaded, or if their outputs are attached to real actuators, one or both of these assumptions are generally invalid. To tune the dynamic behavior of a filter circuit precisely even when assumptions (a) and (b) are relaxed, we thus need **active filters**, as developed in §10.2.

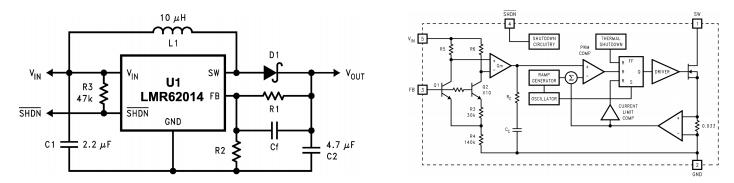

Nevertheless, the simple low-pass and high-pass filters illustrated in Figure 10.3 are useful building blocks for the circuits developed in the remainder of this chapter. As noted in §10.1.3, when excited by a sinusoid (or, by a square wave, which amounts to a sum of sinusoids), the power absorbed by an ideal inductor or capacitor, averaged over a multiple of periods  $T=2\pi/\omega$ , is exactly zero. Thus, in sharp contrast with resistors (which always dissipates power), both inductors and capacitors act like "springs" of sorts, just storing and releasing energy when excited sinusoidally (see Footnote 6 on page 10-4, noting that real inductors and capacitors actually also have a bit of resistance). LC second-order low-pass filters in particular thus operate with very high energetic efficiency, even though their precise dynamic behavior depends on the load applied when assumptions (a) and/or (b) are relaxed. Indeed, when looking at a circuit board of a computer or cyber-physical system, the only place that you will commonly see inductors being used is as low-pass filters in the power regulation circuitry; elsewhere, resistors and capacitors (which are smaller and cheaper) are generally used instead.

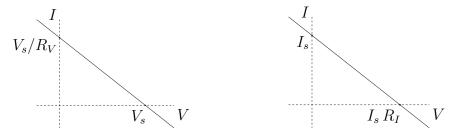

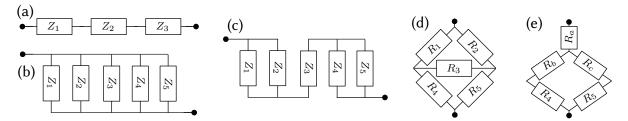

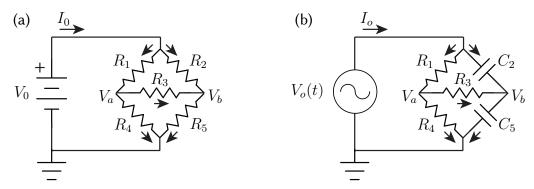

Figure 10.4: (a) Series, (b) parallel, and (c) "reducible" networks of a single type of component, with the  $Z_k$  denoting either resistors  $R_k$ , capacitors  $C_k$ , or inductors  $L_k$ ; (d) a so-called "irreducible" network of resistors, and (e) an equivalent "reducible" network of resistors, with  $\{R_a, R_b, R_c\}$  given by (10.3a).

**Example 10.3 Equivalent resistance, capacitance, and inductance.** The notion of equivalent circuits, with identical current-voltage relationships at one or more pairs of terminals, was defined in Fact 10.1. By the KCL and KVL, it follows that a set of n resistors, capacitors, or inductors in a **series connection** (see Figure 10.4a), in which the current I through the devices is equal and the voltages  $\operatorname{add}^{14}$ ,  $\Delta V_1 + \Delta V_2 + \ldots \Delta V_n = \Delta V$ , have the **equivalent resistance** R, **equivalent capacitance** C, or **equivalent inductance** L, respectively, of:

$$\Delta V_1 = I \, R_1, \quad \Delta V_2 = I \, R_2, \quad \dots \quad \Delta V_n = I \, R_n \quad \Rightarrow \quad \Delta V = I \, R \quad \text{where} \quad R = R_1 + R_2 + \dots R_n,$$

$$\frac{d \, \Delta V_1}{dt} = \frac{I}{C_1}, \quad \frac{d \, \Delta V_2}{dt} = \frac{I}{C_2}, \quad \dots \quad \frac{d \, \Delta V_n}{dt} = \frac{I}{C_n} \quad \Rightarrow \quad \frac{d \, \Delta V}{dt} = \frac{I}{C} \quad \text{where} \quad \frac{1}{C} = \frac{1}{C_1} + \frac{1}{C_2} + \dots \frac{1}{C_n},$$

$$\Delta V_1 = L_1 \frac{dI}{dt}, \quad \Delta V_2 = L_2 \frac{dI}{dt}, \quad \dots \quad \Delta V_n = L_n \frac{dI}{dt} \quad \Rightarrow \quad \Delta V = L \frac{dI}{dt} \quad \text{where} \quad L = L_1 + L_2 + \dots L_n.$$

Similarly, a set of n resistors, capacitors, or inductors in a **parallel connection** (see Figure 10.4b), in which the voltage  $\Delta V$  across the devices is equal and the currents add,  $I_1 + I_2 + \ldots I_n = I$ , have the **equivalent resistance** R, **equivalent capacitance** C, or **equivalent inductance** L, respectively, of:

$$I_{1} = \frac{\Delta V}{R_{1}}, \qquad I_{2} = \frac{\Delta V}{R_{2}}, \qquad \dots \qquad I_{n} = \frac{\Delta V}{R_{n}} \qquad \Rightarrow \qquad I = \frac{\Delta V}{R} \qquad \text{where} \qquad \frac{1}{R} = \frac{1}{R_{1}} + \frac{1}{R_{2}} + \dots + \frac{1}{R_{n}},$$

$$I_{1} = C_{1} \frac{d\Delta V}{dt}, \qquad I_{2} = C_{2} \frac{d\Delta V}{dt}, \qquad \dots \qquad I_{n} = C_{n} \frac{d\Delta V}{dt} \qquad \Rightarrow \qquad I = C \frac{d\Delta V}{dt} \qquad \text{where} \qquad C = C_{1} + C_{2} + \dots + C_{n},$$

$$\frac{dI_{1}}{dt} = \frac{\Delta V}{L_{1}}, \qquad \frac{dI_{2}}{dt} = \frac{\Delta V}{L_{2}}, \qquad \dots \qquad \frac{dI_{n}}{dt} = \frac{\Delta V}{L_{n}} \qquad \Rightarrow \qquad \frac{dI}{dt} = \frac{\Delta V}{L} \qquad \text{where} \qquad \frac{1}{L} = \frac{1}{L_{1}} + \frac{1}{L_{2}} + \dots + \frac{1}{L_{n}}.$$

In "reducible" networks of a single type of components, repeated application of the above simple rules for series and parallel connections of a single type of components is sufficient to determine an equivalent single component value. For example, if the  $Z_k$  in Figure 10.4c denote resistors, then

- the equivalent resistance of the parallel connection of  $R_1$  and  $R_2$  is  $R_a = R_1 R_2 / (R_1 + R_2)$ ,

- the equivalent resistance of the parallel connection of  $R_4$  and  $R_5$  is  $R_b = R_4 R_5/(R_4 + R_5)$ , and

- the equivalent resistance of the entire series connection (of  $R_a$ ,  $R_3$ , and  $R_b$ ) is  $R = R_a + R_3 + R_b$ .

On the other hand, repeated application of the above rules for parallel and series connections of a single type of components is not sufficient to simplify a so-called "irreducible" network, such as that shown in Figure 10.4d, to an equivalent single component value. However, repeated application of the Y- $\Delta$  transformation discussed in Example 10.4 below can often convert such a network to a reducible form, as shown in Figure 10.4e.  $\triangle$

<sup>&</sup>lt;sup>14</sup>In order to apply KVL as stated, visualize a battery connected across the terminals in each of the circuits in Figure 10.4.

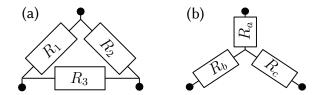

Figure 10.5: Two electrical networks with equivalent voltage/current relationships between their three nodes.

**Example 10.4** The Y- $\Delta$  transformation is an analysis technique for electrical networks based on the equivalent resistance between any two nodes of two different appropriately-configured resistor networks, one shaped like a Y (upside down, sorry) and one shaped like a  $\Delta$ , as shown in Figure 10.5. The relations between the resistors of the  $\Delta$  network and those of the Y network that achieves this equivalence may easily be worked out in Matlab (see code in RR Chapter 10), which results in

$$R_{a} = \frac{R_{1} R_{2}}{R_{1} + R_{2} + R_{3}}, \qquad R_{b} = \frac{R_{1} R_{3}}{R_{1} + R_{2} + R_{3}}, \qquad R_{c} = \frac{R_{2} R_{3}}{R_{1} + R_{2} + R_{3}}, \qquad (10.3a)$$

$$R_{1} = \frac{R_{a} R_{b} + R_{a} R_{c} + R_{b} R_{c}}{R_{c}}, \qquad R_{2} = \frac{R_{a} R_{b} + R_{a} R_{c} + R_{b} R_{c}}{R_{b}}, \qquad R_{3} = \frac{R_{a} R_{b} + R_{a} R_{c} + R_{b} R_{c}}{R_{a}}; \qquad (10.3b)$$

the relations in (10.3a) may be used to determine  $\{R_a, R_b, R_c\}$  from  $\{R_1, R_2, R_3\}$ , and the relations in (10.3b) may be used to determine  $\{R_1, R_2, R_3\}$  from  $\{R_a, R_b, R_c\}$ .

This equivalence may be used, e.g., to convert the "irreducible" network of resistors in Figure 10.4d into the "reducible" network in Figure 10.4e, with  $\{R_a, R_b, R_c\}$  as given in (10.3a), thus upon simplification giving the equivalent resistance R of the entire network in Figure 10.4d as

$$R = R_a + 1/[1/(R_b + R_4) + 1/(R_c + R_5)] = \dots$$

$$= \frac{R_1 R_2 R_3 + R_1 R_2 R_4 + R_1 R_2 R_5 + R_1 R_3 R_5 + R_2 R_3 R_4 + R_1 R_4 R_5 + R_2 R_4 R_5 + R_3 R_4 R_5}{R_1 R_3 + R_1 R_4 + R_2 R_3 + R_1 R_5 + R_2 R_4 + R_2 R_5 + R_3 R_4 + R_3 R_5}.$$

To save significant time at this level (post high school), and to *entirely prevent* algebra mistakes, we may (and, indeed, should!) use **symbolic manipulation** everywhere possible to perform simple algebraic manipulations of systems of equations. We illustrate in RR Chapter 10 two distinct ways of doing this<sup>15</sup>.

One way, as illustrated in the codes associated with, e.g., Examples 10.4 and 10.11, is to list the equations to be solved in a symbolic algebraic form that is easy to read, then to call a sophisticated solver that performs a series of substitutions and rearrangements in order to solve these n equations in the n unknowns specified. Note that this approach works for both linear and (significantly) even certain nonlinear equations.

The other way, illustrated in the codes associated with, e.g., Examples 10.1, 10.2, 10.5, 10.6, 10.10, and 10.12, is designed specifically for linear systems of equations. It first incorporates the n equations to be solved (in n unknowns) as Ax=b, then calls a symbolic version of Gaussian elimination (see §2.2 of NR) to compute the solution x given A and b. Note in particular, in the several examples provided, that well-structured comments in the vicinity of the lines of code that define A and b significantly improve readability, minimizing transcription errors. One of the benefits of this approach is that it is readily apparent under what conditions the set of equations being combined cease to be independent from each other, and thus the matrix A becomes singular, which can be monitored by keeping an eye on the **condition number** (see §2.5 of NR) of A.

<sup>&</sup>lt;sup>15</sup>Of course, following the recommendations of Appendix A, make certain that you comment your codes sufficiently (in English, please!) to make such codes easy to understand and debug.

Figure 10.6: Wheatstone bridges for accurate measurement of (a) resistance, and (b) capacitance.

**Example 10.5 Full analysis of a Wheatstone bridge.** Consider the **Wheatstone bridge** of Figure 10.6a. For convenience, we number the elements of a circuit sequentially, and denote by  $I_k$  the current through element k, with positive current indicated by the direction of the arrow (this keeps us from having to label each current component individually in the figure). The (constant) voltage at the top of the bridge is  $V_0$  (as it is connected to the top of the battery), and the voltage at the bottom of the bridge is 0 (as it is connected to the bottom of the battery, which is defined as ground), thus leaving two undetermined nodal voltages,  $\{V_a, V_b\}$ . We may thus determine the eight unknowns  $\{I_0, I_1, I_2, I_3, I_4, I_5, V_a, V_b\}$  given the six parameters  $\{V_0, R_1, R_2, R_3, R_4, R_5\}$  via KCL at three of the four nodes and the current-voltage relationship across each of the five resistors:

$$I_0 = I_1 + I_2, \quad I_1 = I_3 + I_4, \quad I_2 + I_3 = I_5,$$

(10.4a)

$$V_o - V_a = I_1 R_1, \quad V_o - V_b = I_2 R_2, \quad V_a - V_b = I_3 R_3, \quad V_a = I_4 R_4, \quad V_b = I_5 R_5.$$

(10.4b)

These eight linear equations in the eight unknowns x={I0,I1,I2,I3,I4,I5,Va,Vb} may easily be written in the form Ax=b and solved for x, as illustrated in the corresponding code in RR Chapter 10, which is provided for  $R_1 = R_2 = R_4 = 1$  kohm,  $R_3 = 100$  kohm, and  $V_0 = 5$  V, keeping  $R_5$  as symbolic (all choices that are easily changed), from which it follows immediately that  $I_3 = (1000 - R_5)/(4.06 \times 10^4 R_5 + 4.02 \times 10^7)$  amps. Changing, e.g., to  $R_1 = R_2 = 0$  in this algorithm shows how the resulting system of equations can become singular.

The Wheatstone bridge is particularly useful for the precise measurement of an unknown resistor value (taken here as  $R_5$ ) given three accurately known (often, equal) resister values (taken here as  $\{R_1, R_2, R_4\}$ ), and a center resistor  $R_3$ . Indeed, if  $R_1/R_4 = R_2/R_5$ , then the bridge is said to be **balanced**, and the current through the resister in the center of the bridge,  $I_3$  (which may be measured precisely using a **galvanometer**), will be exactly zero, as  $V_a = V_b$  in this case.

**Example 10.6** A Wheatstone bridge for measuring capacitance. If we simply replace the resistors  $R_2$  and  $R_5$  in Figure 10.6a with capacitors  $C_2$  and  $C_5$ , where  $C_2$  is known and  $C_5$  is unknown, and observe the circuit at steady state, we run into a problem: setting the time derivatives of the current through the capacitors equal to zero (that is, taking  $I_2 = I_5 = 0$ ), it follows that  $I_3 = 0$  and thus  $V_a = V_b$  regardless of the value of  $C_5$ ! Thus,  $C_5$  can *not* be determined in this simplistic manner.

However, as indicated in Figure 10.6b, if we replace resistors  $R_2$  and  $R_5$  with capacitors  $C_2$  and  $C_5$ , and we also replace the constant voltage source with a (sinusoidal) time-varying voltage source, then we can now easily determine  $C_5$ . Our eight equations for the eight unknowns  $\{I_0, I_1, I_2, I_3, I_4, I_5, V_a, V_b\}$  now take the form

$$I_0 = I_1 + I_2, \quad I_1 = I_3 + I_4, \quad I_2 + I_3 = I_5,$$

$V_o - V_a = I_1 R_1, \quad I_2 = C_2 \frac{d(V_o - V_b)}{dt}, \quad V_a - V_b = I_3 R_3, \quad V_a = I_4 R_4, \quad I_5 = C_5 \frac{d(V_b)}{dt},$

where only the equations in blue have changed. Assuming  $R_1=R_2=1$  k $\Omega$ ,  $C_3=10$   $\mu$ F, and  $R_5=100$  k $\Omega$ , that  $\{I_0,I_1,I_2,I_3,I_4,I_5,V_a,V_b,V_o\}$  are all initially zero, taking the Laplace transform [see §10.1.5], and performing

an analogous symbolic manipulation, as shown in the corresponding Wheatstone capacitors code in RR Chapter 10, it follows that, in Laplace transform space,

$$\frac{I_3(s)}{V_0(s)} = G(s) = \frac{(C_5 - C_2)s}{2.01 \times 10^5 (C_5 + C_2)s + 2}.$$

As in the case of drawing Bode plots (see §9.4.1), we are interested in the magnitude and phase of the persistent sinusoidal component of the output current  $I_3(t)$  when the input voltage  $V_0(t)$  is sinusoidal. That is, for the transfer function G(s) given above, taking  $V_0(t) = V \sin(\omega t)$  will result in  $I_3(t) = I \sin(\omega t + \phi) + \text{terms}$  that decay with time, where  $I = |G(i\omega)|$  and  $\phi = \angle G(i\omega)$ , and thus

$$\frac{I}{V} = \frac{|C_5 - C_2| \, \omega}{\sqrt{[2.01 \times 10^5 (C_5 + C_2)]^2 \omega^2 + 4}}, \quad \phi = \begin{cases} 90^\circ - \text{atan2}\{[2.01 \times 10^5 (C_5 + C_2)]\omega, 2\} & \text{if } C_5 > C_2, \\ -90^\circ - \text{atan2}\{[2.01 \times 10^5 (C_5 + C_2)]\omega, 2\} & \text{if } C_5 < C_2. \end{cases}$$

If  $\omega=0$ , then I=0 regardless of  $C_5$ , consistent with the comments made in the previous paragraph. If  $\omega>0$  and I=0, it follows immediately that the bridge is in balance, and thus  $C_5=C_2=10~\mu\text{F}$ . If  $\omega>0$  and  $I\neq 0$ ,  $C_5$  may be determined from I according to the above expressions (with  $C_5>C_2$  if  $\phi>0$ , and  $C_5< C_2$  if  $\phi<0$ ; note the  $180^\circ$  phase shift in  $\phi$  when  $C_5$  is changed from below  $C_2$  to above  $C_2$ ). Inductance may be quantified with a Wheatstone bridge in an analogous fashion (see Exercise 10.2).  $\triangle$

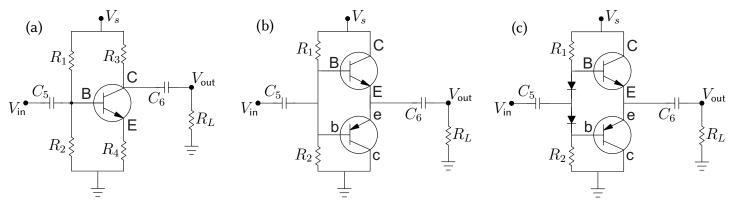

**Example 10.7 Equivalent sources** Any combination of voltage sources, current sources, and resistors leads to a linear current-voltage relationship like those in Figure 10.2; the following facts follow as consequence.

Fact 10.4 (Thévenin's theorem) Any circuit containing only voltage sources, current sources, and resistors can be converted to a Thévenin equivalent circuit, with one ideal voltage source and one resistor in series.

**Fact 10.5 (Norton's theorem)** Any circuit containing only voltage sources, current sources, and resistors can be converted to a **Norton equivalent circuit**, with one ideal current source and one resistor in parallel.

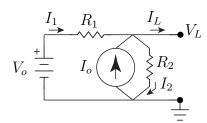

Figure 10.7: A circuit with both voltage and current sources as well as two resistors.

To illustrate, consider the circuit shown in Figure 10.7. Writing down KCL at the node at the top of the circuit and Ohm's law across each resistor, the (linear) current-voltage relationship at the terminals may be determined:

$$\begin{vmatrix}

I_1 + I_o = I_L + I_2 \\

V_o - V_L = I_1 R_1 \\

V_L = I_2 R_2

\end{vmatrix}

\Rightarrow I_L = I_o + I_1 - I_2 = \left(I_o + \frac{V_o}{R_1}\right) - \left(\frac{1}{R_1} + \frac{1}{R_2}\right) V_L.$$

(10.5)

It follows from this analysis of the circuit in Figure 10.7 that

- its Thévenin equivalent (Figure 10.1e) sets  $R_V = R_1 R_2/(R_1 + R_2)$  and  $V_s = (I_o + V_o/R_1)R_V$ , and

- its Norton equivalent (Figure 10.1f) sets  $R_I = R_1 R_2 / (R_1 + R_2)$  and  $I_s = I_o + V_o / R_1$ ;

note that all of these circuits have identical current-voltage relationships, as illustrated in Figure 10.2.

$\triangle$

Of particular interest in this example is the question of how much power is actually provided by the two sources in Figure 10.7. To simplify, assume first that  $R_1 = I_L = 0$ ; in this case,  $V_L = V_o$ , and

- the power absorbed by the current source is  $-I_oV_o < 0$  (that is, power is *provided* by the current source regardless of the relative magnitudes of  $I_o$  and  $V_o/R_2$ ), whereas

- the power absorbed by the voltage source is  $-I_1V_o = -(I_2 I_o)V_o = -(V_o/R_2 I_o)V_o$  (that is, power is *provided* by the voltage source if  $V_o/R_2 > I_o$ , and is *absorbed* by the voltage source if  $V_o/R_2 < I_o$ ).

Taking  $R_1 > 0$  and  $I_L \neq 0$ , similar conclusions may be drawn (see Exercise 10.3).

### 10.1.5 Laplace transform analysis of circuits and the definition of impedance

In simple circuits without capacitors or inductors, combining KCL and the current-voltage relationship across each component leads to straightforward systems of *linear algebraic equations*, which may be solved by hand or with symbolic numerical tools. In more interesting circuits incorporating capacitors and/or inductors, combining KCL and the current-voltage relationship across each component often leads, more generally, to sets of *linear constant-coefficient ODEs* together with various algebraic constraints (jointly referred to as **descriptor systems**). Without the Laplace transform, as developed in §9, the analysis of such systems would be difficult. However, as seen in the various examples presented above, application of the Laplace transform to such systems converts them back to straightforward systems of algebraic equations, incorporating the Laplace transform variable s, that are again easy to solve by hand or with simple symbolic numerical tools.

It is thus seen that, when analyzing electric circuits, working in the Laplace domain is essential. Further, one is often interested in the frequency response of an electric circuit subject to sinusoidal excitation. As shown in §9.4.1, the gain and phase shift of the persistent sinusoidal component of the output of a linear system G(s) when excited by a sinusoidal input may be summarized by the Bode plot of G(s), and may be calculated simply by evaluating the magnitude and phase of  $G(i\omega)$  as a function of the frequency  $\omega$  of the input sinusoid.

**Example 10.8 Impedance of the fundamental circuit elements.** Taking the Laplace transform of the current-voltage relationships of resistors, capacitors, and inductors [see (10.2)] and evaluating at  $s = i \omega$  gives

$$G_{\text{resistor}}(\mathrm{i}\omega) = \frac{V(\mathrm{i}\omega)}{I(\mathrm{i}\omega)} = R \triangleq Z_R, \quad G_{\text{capacitor}}(\mathrm{i}\omega) = \frac{V(\mathrm{i}\omega)}{I(\mathrm{i}\omega)} = \frac{-\mathrm{i}}{\omega\,C} \triangleq Z_C, \quad G_{\text{inductor}}(\mathrm{i}\omega) = \frac{V(\mathrm{i}\omega)}{I(\mathrm{i}\omega)} = \mathrm{i}\,\omega\,L \triangleq Z_L.$$

The quantities  $Z_R$ ,  $Z_C$ , and  $Z_L$  are used often, and are commonly referred as the **impedance** of each of these components. In other texts, the concept of impedance is often discussed somewhat loosely as a *complex*, frequency-dependent generalization of resistance even before Laplace transforms are properly introduced. This approach is, perhaps, unnecessarily convoluted; pedagogically, the author recommends instead mastering the Laplace transform (§9.2) and Bode plot (§9.4.1) before reading the present discussion (and that which follows); the frequency response of the current-voltage relationships represented by the (complex) transfer functions  $G_{\text{resistor}}(s)$ ,  $G_{\text{capacitor}}(s)$ , and  $G_{\text{inductor}}(s)$  as listed above [and,  $G_{\text{speaker}}(s)$  and  $G_{\text{piezo}}(s)$ , as discussed in Examples 10.9 and 10.10 below] are then quite easy to interpret. In particular, these characterizations are consistent with the phenomenological description of the general behavior of capacitors and inductors given in §10.1.3.1:

- the voltage across a capacitor lags the current through the capacitor by 1/4 cycle [ $\phi = -90^{\circ}$ , associated with the -i factor in  $G_{\rm capacitor}(i\,\omega)$ ], with the magnitude of the sinusoidal voltage across the capacitor divided by the magnitude of the sinusoidal current through the capacitor decreasing with frequency  $\omega$ ;

- the voltage across an inductor leads the current through the inductor by 1/4 cycle [ $\phi = 90^{\circ}$ , associated with the i factor in  $G_{\rm inductor}(i\,\omega)$ ], with the magnitude of the sinusoidal voltage across the inductor divided by the magnitude of the sinusoidal current through the inductor increasing with frequency  $\omega$ .

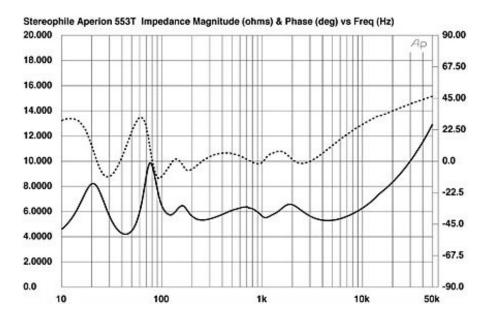

Figure 10.8: Bode plot of the transfer function  $G(s) = V(\mathrm{i}\,\omega)/I(\mathrm{i}\,\omega)$  from current to voltage, also referred to as the **impedance**, of a Aperion Audio Intimus 533-T loudspeaker. The horizontal axis is the log of the frequency in Hz (not rad/s, which is typical in controls). The solid curve indicates the magnitude, with its (linear) scale at left; note the magnitude is around 6 ohms (varying between about 5.3 ohms and 6.7 ohms) over audio frequencies from 100 Hz to 10 kHz. The dotted curve indicates the phase, with scale at right in units of degrees; note the phase is around  $0^\circ$  (varying between about - $10^\circ$  and  $23^\circ$ ) over audio frequencies from 100 Hz to 10 kHz. Plot courtesy of Stereophile.com.

Example 10.9 Impedance of an audio speaker. Figure 10.8a illustrates the Bode plot of the transfer function  $G_{\text{speaker}}(s) = V(s)/I(s)$ , from current to voltage, of a typical audio speaker. This plot is commonly referred to as the (frequency-dependent) impedance of the speaker. If this device presented a purely resistive load to the electric circuit, the magnitude of the impedance (measured in ohms; 4 ohm, 6 ohm, and 8 ohm speakers are common) would be constant across all frequencies, and its phase would be zero. However, a speaker is of course *not* a simple resistive load; rather, its Bode plot depends on the mechanical and electrical details of its construction. Nevertheless, over typical audio frequencies (from 100 Hz to 10 kHz), it is seen that this speaker approximates a simple resistive load of around 6 ohm. Looking a bit more closely, the magnitude part of this Bode plot,  $|G(i\omega)|$ , reveals peaks and valleys ("resonances" and "antiresonances") as a function of frequency, and the phase part of this Bode plot is generally somewhat positive wherever  $|G(i\omega)|$  is increasing with  $\omega$ , and somewhat negative wherever  $|G(i\omega)|$  decreases with with  $\omega$ .

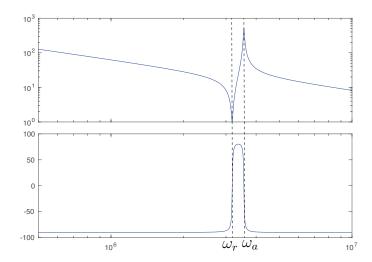

Figure 10.9: Bode plot of the transfer function  $G(s) = V(\mathrm{i}\,\omega)/I(\mathrm{i}\,\omega)$  from current to voltage, also referred to as the **impedance**, of the Butterworth/van Dyke circuit model of a piezoelectric material. The system is said to be essentially **inductive** ( $\phi \approx 90^\circ$ ) for  $\omega_r < \omega < \omega_a$ , and essentially **capacitive** ( $\phi \approx -90^\circ$ ) outside this range.

Figure 10.10: The Butterworth/van Dyke circuit model of a piezoelectric material, as considered in Example 10.10.

**Example 10.10 Impedance of piezos.** Many crystalline materials, such as quartz crystals, exhibit a **piezo-electric effect** such that

- when a voltage is applied across the material, it mechanically deforms, and

- when the material is deformed, a charge accumulates on its surface that generates a measurable voltage.

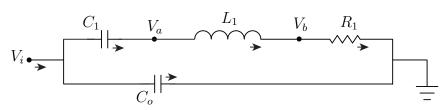

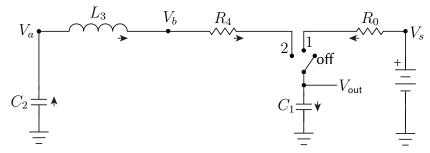

Electromechanical devices (both sensors and actuators) that exhibit strong resonant oscillations may be constructed using such piezoelectric materials. A model electric circuit capturing the essence of such electromechanical devices is illustrated in Figure 10.10. The (Laplace-transformed) equations governing this circuit are

$$I_i = I_o + I_1, \quad I_o = C_o s V_i, \quad I_1 = C_1 s [V_i - V_a], \quad [V_a - V_b] = s L_1 I_1, \quad V_b = R_1 I_1;$$

that is, 5 eqns in the 5 variables  $\mathbf{x}(s) = \{I_o(s), I_1(s), V_i(s), V_a(s), V_b(s)\}$ , treating the current  $I_i(s)$  as an input and  $\{C_o, C_1, L_1, R_1\}$  as parameters. Solving (see the corresponding code in RR Chapter 10) gives

$$G_{\text{piezo}}(s) = \frac{V_i(s)}{I_i(s)} = \frac{L_1 C_1 s^2 + R_1 C_1 s + 1}{s \left(L_1 C_o C_1 s^2 + R_1 C_o C_1 s + C_o + C_1\right)} = K \frac{s^2 + 2 \zeta_r \omega_r s + \omega_r^2}{s \left(s^2 + 2 \zeta_a \omega_a s + \omega_a^2\right)},$$

where  $\omega_r=1/\sqrt{L_1\,C_1},~\zeta_r=R_1/(2\,\omega_r\,L_1),~\omega_a=1/\sqrt{L_1\,C_a}$  with  $C_a=C_o\,C_1/(C_o+C_1),~\zeta_a=R_1/(2\,\omega_a\,L_1),~K=1/C_o$ ; for  $\{C_o,C_1,L_1,R_1\}=\{2\,\mathrm{nF},0.5\,\mathrm{nF},5\,\mu\mathrm{H},1\,\mathrm{ohm}\},$  the Bode plot of  $G_{\mathrm{piezo}}(s)$  is given in Figure 10.8b, indicating a lightly-damped resonance and antiresonance at  $\omega_r=3.18\,\mathrm{MHz}$  and  $\omega_a=3.56\,\mathrm{MHz}.$

Figure 10.11: The **LC tank oscillator** considered in Example 10.11.

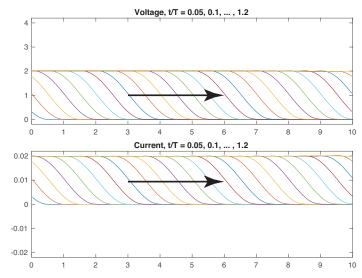

**Example 10.11 LC tank oscillator.** We now consider the oscillator circuit in Figure 10.11, initialized with the switch in the **off** position, current equal to zero everywhere, and all capacitors fully discharged.

**Startup.** At t=0, with  $V_{\text{out}}(t=0)=0$ , we turn the switch from off to **position 1**. Current flows from the battery, at voltage  $V_s$ , through  $R_0$ , through  $C_1$ , to ground. Denoting the current through component i as  $I_i(t)$ , with positive current in the direction of the arrows shown, KCL and the component equations for  $R_0$  and  $C_1$  are

$$I_0(s) = I_1(s), \quad V_s - V_{\text{out}}(s) = R_0 I_0(s), \quad s C_1 V_{\text{out}}(s) = I_1(s).$$

These three eqns in  $\{I_0(s), I_1(s), V_{\text{out}}(s)\}$  are easily reduced to one eqn in  $V_{\text{out}}(s)$ , and inverse transformed:

$$[V_s - V_{\text{out}}(s)]/R_0 = s C_1 V_{\text{out}}(s) \Rightarrow [(1 + R_0 C_1 d/dt) V_{\text{out}}(t) = V_s, V_{\text{out}}(t=0) = 0].$$

This inhomogeneous linear ODE has a homogeneous solution of  $V_{\text{out}}(t) = A \, e^{-t/(R_0 C_1)}$  and a particular solution of  $V_{\text{out}}(t) = V_s$ . Summing these two solutions and matching the ICs (by taking  $A = -V_s$ ) gives the full solution

$$V_{\text{out}}(t) = V_s(1 - e^{-t/(R_0 C_1)}).$$

(10.6a)

By the component equations for both  $R_0$  and  $C_1$ , the corresponding current  $I_0(t) = I_1(t) \triangleq I(t)$  is

$$I(t) = [V_s - V_{\text{out}}(t)]/R_0 = C_1 dV_{\text{out}}(t)/dt \quad \Rightarrow \quad I(t) = (V_s/R_0) e^{-t/(R_0 C_1)}. \tag{10.6b}$$

The responses of  $V_{\text{out}}(t)$  and I(t) are characterized by exponential decay, with

$$V_{\text{out}}(t) \to V_{\text{s}} \quad \text{and} \quad I(t) \to 0 \quad \text{as} \quad t \to \infty.$$

(10.6c)

If you know values for  $\{V_s, R_0, C_1\}$ , the time  $t_s$  after which  $V_{\text{out}}(t)$  settles to within, say, 95% of its steady state value is given by setting  $0.95 V_o = V_o (1 - e^{-t/(R_0 C_1)})$  and solving for t, giving

$$t = -R_0 C_1 \ln(0.05) \approx 3 R_0 C_1. \tag{10.6d}$$

**Decaying oscillations.** Starting from the steady-state values of  $V_{\text{out}}(t)$  and I(t) determined in (10.6c), we now move the switch from position 1 to **position 2**. [For simplicity, we also reset the clock, so that t=0 now corresponds to the time that we flip the switch to position 2.] KCL now gives

$$I_2(t) = I_3(t) = I_4(t) = I_1(t) \triangleq I(t).$$

(10.7)

Note also that the Laplace transform of  $V'_{\rm out}(t)=d[V_{\rm out}(t)]/dt$  is  $V'_{\rm out}(s)=s\,V_{\rm out}(s)-V_s$ , due to its nonzero ICs. Implementing KCL, given above, into the Laplace transform of the component equations for  $\{C_1,C_2,L_3,R_4\}$ , we have four eqns with three intermediate variables,  $\{I(s),V_a(s),V_b(s)\}$ , to be eliminated:

$$I(s) = s C_2 [-V_a(s)], \quad V_a(s) - V_b(s) = s L_3 I(s), \quad V_b(s) - V_{\text{out}}(s) = R_4 I(s), \quad I(s) = C_1 [s V_{\text{out}}(s) - V_s].$$

Reducing these four algebraic eqns in the four variables  $\{I(s), V_a(s), V_b(s), V_{\text{out}}(s)\}$  to one eqn in  $V_{\text{out}}(s)$  is easily done by hand (or, better, in Matlab; see code in RR Chapter 10), giving immediately:

$$V_{\text{out}}(s) = \frac{b_2 s^2 + b_1 s + b_0}{s[s^2 + a_1 s + a_0]} \quad \text{with}$$

$$a_1 = \frac{R_4}{L_3}, \quad a_0 = \frac{1}{L_3 C}, \quad \frac{1}{C} = \frac{1}{C_1} + \frac{1}{C_2} = \frac{C_1 + C_2}{C_1 C_2}, \quad b_2 = V_s, \quad b_1 = \frac{V_s R_4}{L_3}, \quad b_0 = \frac{V_s}{L_3 C_2}.$$

$$(10.8)$$

Noting the  $e^{-\sigma t}\cos(\omega_d t)$  and  $e^{-\sigma t}\sin(\omega_d t)$  entries in Table 9.1, and setting

$$s^2 + a_1 s + a_0 = (s + \sigma)^2 + \omega_d^2 = s^2 + 2 \sigma s + (\sigma^2 + \omega_d^2) \quad \Rightarrow \quad \sigma = a_1/2, \quad \omega_d = \sqrt{a_0 - a_1^2/4},$$

we may rewrite (10.8) via partial faction expansion as

$$V_{\text{out}}(s) = \frac{b_2 s^2 + b_1 s + b_0}{s \left[ (s+\sigma)^2 + \omega_d^2 \right]} = B_2 \frac{1}{s} \cdot \frac{(s+\sigma)^2 + \omega_d^2}{(s+\sigma)^2 + \omega_d^2} + B_1 \frac{(s+\sigma)}{(s+\sigma)^2 + \omega_d^2} \cdot \frac{s}{s} + B_0 \frac{\omega_d}{(s+\sigma)^2 + \omega_d^2} \cdot \frac{s}{s}. \tag{10.9}$$

This may be solved for  $\{B_2, B_1, B_0\}$  by forming a common denominator, as shown above, and setting like powers of s in the numerator as equal (see corresponding code in RR Chapter 10), which immediately gives

$$B_2 = \frac{b_0}{\sigma^2 + \omega_d^2}, \ B_1 = b_2 - B_2, \ B_0 = \frac{b_1 - b_2 \sigma}{\omega_d} - B_2 \frac{\sigma}{\omega_d}.$$

Thus, for  $t \geq 0$ ,

$$V_{\text{out}}(t) = B_2 + B_1 e^{-\sigma t} \cos(\omega_d t) + B_0 e^{-\sigma t} \sin(\omega_d t),$$

(10.10a)

$$I(t) = C_1 dV_{\text{out}}(t)/dt = C_1 e^{-\sigma t} [(-\sigma B_1 + \omega_d B_0) \cos(\omega_d t) + (-\sigma B_0 - \omega_d B_1) \sin(\omega_d t)], \tag{10.10b}$$

where the constants  $\{\omega_d, \sigma, B_2, B_1, B_0\}$  depend on  $\{V_s, R_0, C_1, C_2, L_3, R_4\}$  via the various equations above.

If  $R_4=0$  and  $C_1=C_2$ , then  $C/C_1=C/C_2=1/2$ ,  $a_1=b_1=\sigma=B_0=0$ , and  $B_2=B_1=V_s/2$ , and thus a sort of balanced "see-saw" effect sets in, with

$$V_{\text{out}}(t) = V_s[1 + \cos(\omega_d t)]/2, \qquad I(t) = -(C_1 V_s/2) \,\omega_d \sin(\omega_d t),$$

$$V_a(t) = V_{\text{out}}(t) + [L_3 \,d/dt]I(t) = (V_s/2)[1 + \cos(\omega_d t) - L_3 \,C_1 \,\omega_d^2 \cos(\omega_d t)] = V_s[1 - \cos(\omega_d t)]/2];$$

that is, the charge shifts from  $C_1$  to  $C_2$  (i.e., from  $V_{\text{out}}$  to  $V_a$ ), and back, sinusoidally (undamped) over the period

$$T = 2\pi/\omega_d = 2\pi\sqrt{L_3C} \implies T = 2\pi\sqrt{L_3C_1C_2/(C_1 + C_2)}.$$

Again, there will always be some resistance in practical capacitors and inductors; we model its net effect in this circuit with the (small) resistor  $R_4$ . Any such resistance (e.g., taking  $R_4 > 0$ ) will result in  $\sigma > 0$ , and thus cause the oscillations to decay in time. This decay may be offset with an op amp, as explored in Example 10.32.  $\triangle$

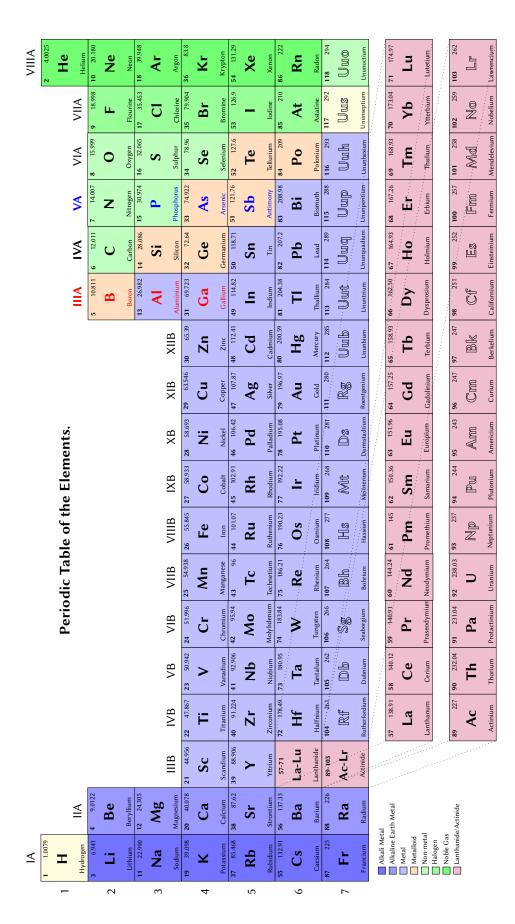

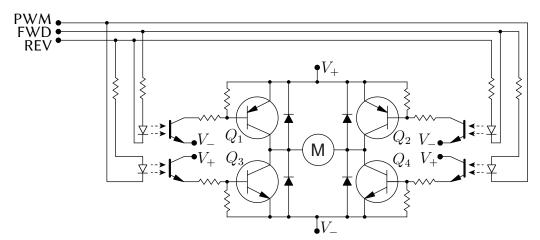

Figure 10.12: Periodic Table of the Elements, for providing context related to the structure of common semiconductors. Carbon, Silicon, and Germanium, which are all in column IVA (that is, the "carbon column"), crystallize in a diamond crystal structure. Gallium arsenide (equal parts Gallium, from column IIIA, and Arsenic, from column VA), crystallizes in a zincblende crystal structure, which is simply a diamond crystal structure with gallium and arsenic in alternating lattice sites. Silicon carbide can take any of about 250 crystalline forms, including zincblende. Note that n-type dopants, such as phosphorus, arsenic, or antimony, are taken from column VA (just to the right of the carbon column), thus introducing extra valence electrons (not bound by the crystal structure) that can move fairly easily when a voltage is applied. Similarly, p-type dopants, such as boron, aluminum, or gallium, are selected from column IIIA (just to the left of the carbon column), thuus introducing "holes" in the crystal's electron structure that can also move fairly easily when a voltage is applied.

# 10.2 Active analog circuits & filters

#### 10.2.1 Semiconductor circuit elements

A **semiconductor** is a material (often, a single crystal<sup>16</sup>) that has conduction properties that may be tuned during fabrication in various useful ways. A single pure crystal of semiconductor material, such as silicon (see Figure 10.12), is generally nonconductive, as all of the **valence** (outer-shell) electrons of the constituent atoms are tied up by the **covalent bonds** of the crystal.

However, if a semiconductor crystal is formed, or **doped**, with **n-type dopant** atoms such as **phosphorus** (see Figure 10.12), an extra valence electron is introduced in the crystal lattice for each atom of the n-type dopant in the crystal. These extra valence electrons can move fairly easily when a voltage is applied across the material, thus making an n-doped semiconductor, such as phosphorus-doped silicon, a conductor.

Similarly, if a semiconductor crystal is formed with **p-type dopant** atoms such as **boron** (see Figure 10.12), a valence electron is missing from the crystal lattice for each atom of the p-type dopant present in the crystal, forming what is known as a "**hole**" in the electron structure of the crystal. These holes in the electron structure of the crystal can also move fairly easily when a voltage is applied across the material, thus making a p-doped semiconductor, such as boron-doped silicon, also a conductor.

### 10.2.1.1 p-n junctions & diodes

When a semiconductor crystal has various neighboring sections, some that are p-doped and some that are n-doped, thus forming **p-n junctions** within the semiconductor, useful electrical characteristics arise. For example, a semiconductor crystal which has just two adjacent doped regions, with a single p-n junction in the middle, is called a **semiconductor diode**, which behaves in the ideal setting as follows:

- If a semiconductor diode is put under **forward bias**, with positive voltage applied to the p side of the semiconductor and negative voltage applied to the n side, then electrons will flow into the n side of the semiconductor, pushing free valence electrons in the crystal lattice towards the p-n junction. These electrons, in turn, flow into the nearby holes on the p side of the semiconductor and create, in effect, a flow holes on the p side of the semiconductor that is equal in magnitude and opposite in direction to the flow of electrons on the n side of the semiconductor, thus sustaining an electric current through the material with very little (ideally, zero) resistance 18.

- If a semiconductor diode is put under **reverse bias**, with positive voltage applied to the n side of the semiconductor and negative voltage applied to the p side, then some of the extra valence electrons on the n side of the semiconductor are pulled away from the p-n junction and out of the semiconductor, and some of the holes in the electron structure of the crystal on the p side of the semiconductor are pulled away from the p-n junction and, effectively, out of the semiconductor, creating a so-called **depletion layer** with neither holes nor free valence electrons to carry moving charge (that is, to sustain the current) in the vicinity of the p-n junction. As a result, an ideal diode under negative bias does not conduct.

<sup>&</sup>lt;sup>16</sup>**Amorphous** semiconductors, which lack a long-range ordered crystal structure, can also be manufactured, and can be done so in especially thin layers over large areas. Such semiconductors may be doped in a manner similar to the single-crystal semiconductors discussed in §10.2.1, and can be switched from one physical state to another (e.g., from translucent to opaque), which makes them especially useful in a variety of applications, such as **CDs/DVDs/BDs**, **liquid-crystal displays** (**LCDs**), and **solar cells**.

<sup>&</sup>lt;sup>17</sup>Note that it is actually a neighboring electron in the electron structure of a crystal lattice that moves, thereby changing the "hole" location in this electron structure; several successive movements of electrons into neighboring hole locations give the appearance that it is the hole itself that is moving.

<sup>&</sup>lt;sup>18</sup>As a loose physical analogy of current flow in a diode under forward bias, one might visualize the electron motion (on the n-doped side) towards the p-n junction as tiny drops of rain falling through air toward an air/water interface, and the corresponding hole motion (on the p-doped side) towards the p-n junction as tiny bubbles of air rising through water toward the air/water interface at the same rate, resulting in zero net accumulation of negative or positive charge (raindrops or bubbles) at the interface.

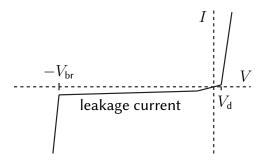

Figure 10.13: Typical current-voltage relationship of a real diode, with forward bias given by V>0 and reverse bias given by V<0, indicating the **breakdown voltage**  $V_{\rm br}$ , the leakage current, and the **cut-in voltage**  $V_d$ .

Though the ideal model of a semiconductor diode described above is sometimes adequate, the deviations of real semiconductor diodes from this behavior, as indicated in Figure 10.13, are important to quantify:

- Within the depletion layer described above in the reverse bias setting, the n-doped side, now lacking its extra valence electrons, is positively charged, and the p-doped side, now lacking its holes, is negatively charged by the same amount. This sets up an electric field across the p-n junction. When the applied voltage exceeds a certain **breakdown threshold**  $V_{\rm br}$  (typically 5 to 20 volts), one of two phenomena occurs (which phenomena sets in first depends on various particular details of the diode).

- In **Zener breakdown**, this electric field directly breaks some of the covalent bonds in the semiconductor crystal, thus allowing the resulting freed electrons to act as charge carriers.

- In avalanche breakdown, on the other hand, the electric field accelerates free valence electrons near the edge of the depletion layer to sufficient energies that their subsequent collision with bound electrons can break covalent bonds within the depletion layer, resulting in the creation of additional charge carriers (pairs of free electrons and holes), which in turn collide with other bound electrons within the depletion layer to create still more charge carriers, etc.

Note that avalanche breakdown is **hysteretic** (that is, after it sets in and the additional charge carriers are created within the depletion layer, the semiconductor continues to conduct even after the voltage is reduced below the breakdown threshold), whereas Zener breakdown is not. Diodes designed to undergo these types of breakdown at specific voltages without being damaged, called **Zener diodes** and **avalanche diodes** respectively, are both useful in electric circuit design.

- **Diffusion** of charge carriers (electrons and holes) across the p-n junction in a diode sets up a small depletion zone and a corresponding **built-in voltage** even when the external voltage applied to the diode is zero. Thus, under forward bias, the applied voltage must exceed a certain **cut-in voltage**  $V_{\rm d}$  (0.6 to 0.7 V for silicon diodes, 0.25 to 0.3 V for germanium diodes, and 0.15 to 0.45 volts for Schottky diodes) before current will begin to flow.

- Due to a weak thermodynamic process of **carrier generation and recombination** inside the depletion layer, a small **leakage current** always flows through a diode under reverse bias even when the applied voltage is below the breakdown threshold. Note in particular that

- carrier generation due to the absorption of energy of incident photons, and the resulting current when under forward bias, is how **photodiodes** respond to the intensity of incident light, whereas

- in **light-emitting diodes** (**LED**s), during **carrier recombination**, energy is released as photons.

- Finally, under both forward bias (with the applied voltage exceeding the cut-in voltage) and reverse bias (with the applied voltage exceeding the breakdown threshold), a diode exhibits a very small amount of electrical **resistance**, thus creating a very steep slope in a plot of *I* versus *V* (see Figure 10.13).

Regular diodes are denoted by the symbol  $\rightarrow$  , and both avalanche and Zener diodes by the symbol  $\rightarrow$  , with the arrow pointing in the direction of the current when under forward bias. Real semiconductor diodes are often **axial** (small cylinders with a wire out each end), with the n-doped end marked with a single bar, consistent with the bar at the end of the diode symbol.

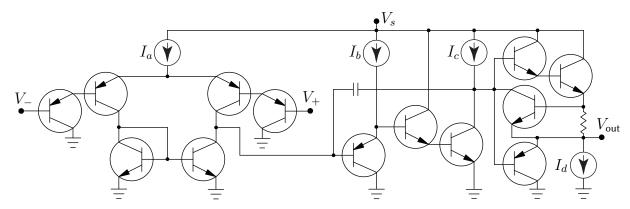

#### 10.2.1.2 Bipolar Junction Transistors (BJTs)

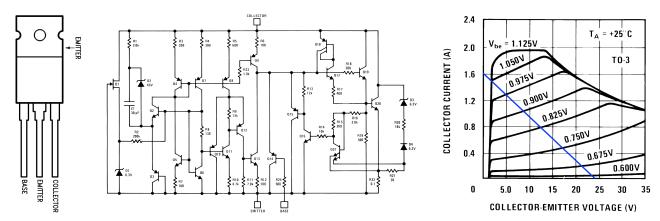

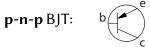

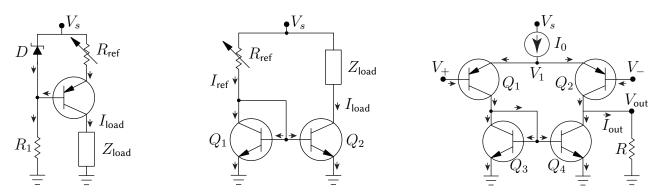

A semiconductor crystal designed to behave as an **amplifier** or an **electronically-activated switch** is called a **transistor**, and is built from three adjacent doped regions of alternating type. As depicted in Table 10.7, there are essentially eight main types of transistors, which are all somewhat similar in their application, though they differ considerably in their physical construction and internal operation. A **bipolar junction transistor** (**BJT**) is the most robust and common type of transistor. A BJT is, in effect, two oppositely-facing diodes placed back-to-back in a single semiconductor crystal. As suggested by their respective names and symbols,

- in a p-n-p type BJT, the emitter-base connection is a p-n diode nominally under forward bias, whereas

- in an n-p-n type BJT, the base-emitter connection is a p-n diode nominally under forward bias.

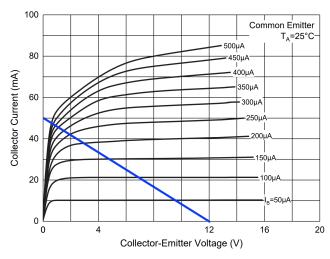

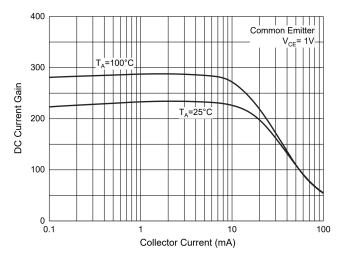

If the middle section of a BJT, called the **base**, is left unconnected, then (in the ideal setting, assuming no breakdown) there will be zero current between the two ends of the BJT (called the **emitter** and the **collector**), as one of its two p-n junctions will always be under reverse bias. If (in the p-n-p case) a small **emitter**  $\rightarrow$  **base** current (or, in the n-p-n case, a small **base**  $\rightarrow$  **emitter** current) is initiated, this populates the central region of the transistor (including the depletion zone in the p-n junction between the base and the collector, which is nominally under reverse bias) with charge carriers, thus causing a much larger current between the emitter and collector to flow, proportional to the current at the base. We denote the voltages and the magnitude of the currents of the emitter, base, and collector as, respectively,  $\{V_{\rm E}, V_{\rm B}, V_{\rm C}\}$  and  $\{I_{\rm E}, I_{\rm B}, I_{\rm C}\}$ ; note that  $I_{\rm E} = I_{\rm C} + I_{\rm B}$  in both n-p-n and p-n-p type BJTs. Assuming the voltage differences are sufficiently small that breakdown does not set in, the three useful modes of operation of a **n-p-n transistor** depend on where  $V_B$  is with respect to  $V_C$  and  $V_E$ , with  $V_C > V_E$  (the p-n-p case is similar, with all inequalities reversed):

- **Saturation** or "on" mode:  $V_B > V_C > V_E$ . Both p-n junctions are forward biased; current flows freely (small effective resistance  $R_{CE(on)}$ ), limited by resisters elsewhere in the circuit. Energetically efficient!

- Forward active or "linear" mode:  $V_{\rm C} > V_{\rm B} > V_{\rm E}$ . This is the nominal setting in which the transistor acts as a current amplifier, as used in many audio systems. The current gain from  $I_{\rm B}$  to  $I_{\rm C}$  in this mode is denoted  $h_{\rm FE}$  or  $\beta_{\rm F}$ , and is typically about  $h_{\rm FE} = \beta_{\rm F} = I_{\rm C}/I_{\rm B} \approx 100$ , whereas the ratio  $I_{\rm C}/I_{\rm E}$  is denoted  $\alpha_{\rm F}$ , and is typically about  $\alpha_{\rm F} = I_{\rm C}/I_{\rm E} = \beta_{\rm F}/(1+\beta_{\rm F}) \approx 0.99$ . Not energetically efficient.

- Cutoff mode:  $V_C > V_E > V_B$ . Both p-n junctions are reverse biased; very little current flows. Efficient!

| Bipolar Junction          |            | Field-Effect Transistor ( <b>FET</b> ) |                    |                                     |           |                  |           |  |  |

|---------------------------|------------|----------------------------------------|--------------------|-------------------------------------|-----------|------------------|-----------|--|--|

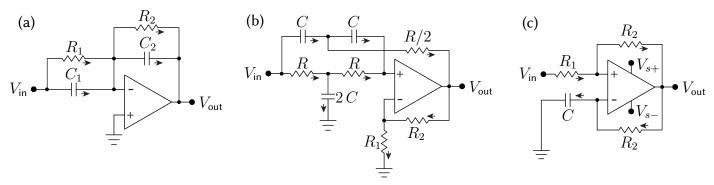

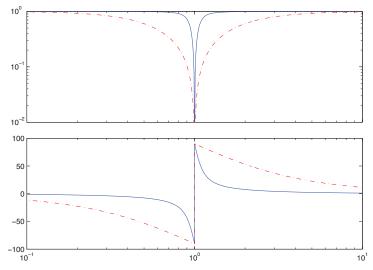

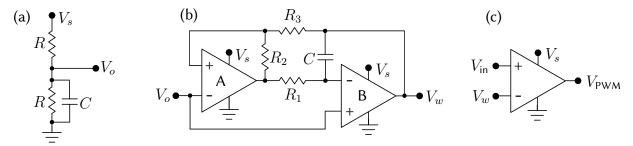

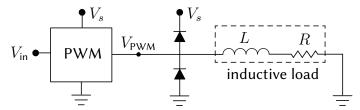

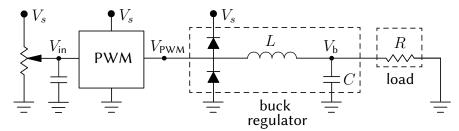

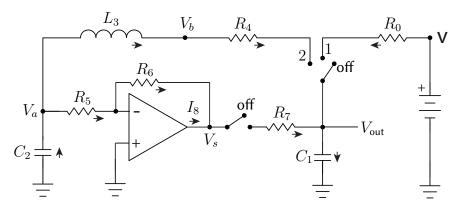

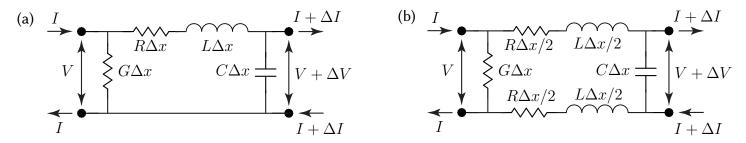

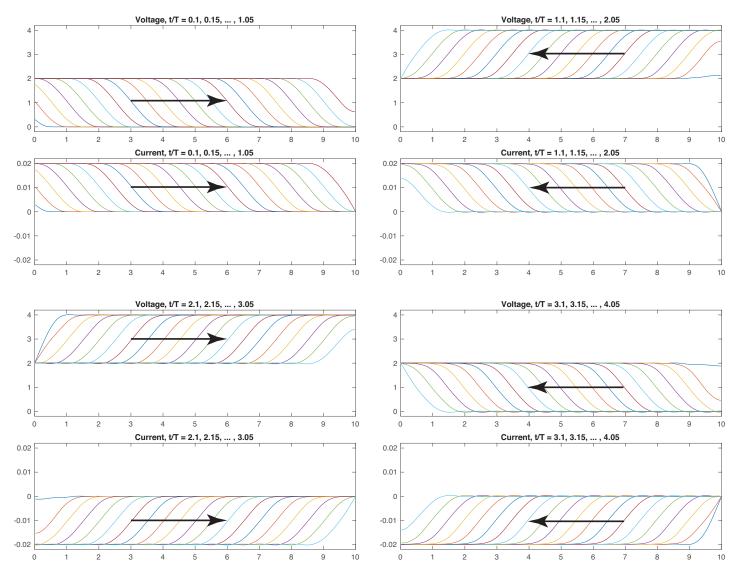

| Transistor ( <b>BJT</b> ) |            | Junction F                             | ET ( <b>JFET</b> ) | Insulated-Gate FET ( <b>IGFET</b> ) |           |                  |           |  |  |